Chapter: Embedded Systems

Component Interfacing: Memory and Device Interfacing

COMPONENT INTERFACING

Building

the logic to interface a device to a bus is not too difficult but does take

some attention to detail. We first consider interfacing memory components to

the bus, since that is relatively simple, and then use those concepts to

interface to other types of devices.

Memory Interfacing

If we can

buy a memory of the exact size we need, then the memory structure is simple. If

we need more memory than we can buy in a single chip, then we must construct

the memory out of several chips. We may also want to build a memory that is

wider than we can buy on a single chip; for example, we cannot generally buy a

32- bit-wide memory chip. We can easily construct a memory of a given width (32

bits, 64 bits, etc.) by placing RAMs in parallel.

We also

need logic to turn the bus signals into the appropriate memory signals. For

example, most busses won’t send address signals in row and column form. We also

need to generate the appropriate refresh signals.

Device Interfacing

Some I/O

devices are designed to interface directly to a particular bus, forming

glueless interfaces. But glue logic is required when a device is connected to a

bus for which it is not designed.

An I/O device typically requires a much smaller

range of addresses than a memory, so addresses must be decoded much more

finely. Some additional logic is required to cause the bus to read and write

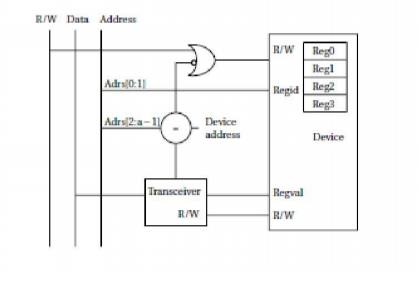

the device’s registers. Example 4.1 shows one style of interface logic.

Example

A glue

logic interface

Below is

an interfacing scheme for a simple I/O device

The device has four registers that can be read and

written by presenting the register number on the regid pins, asserting R/W as required, and reading or writing the

value on the regval pins.

Related Topics