Chapter: Embedded Systems Design : Embedded processors

Sun SPARC RISC processor

Sun SPARC RISC processor

The SPARC (scalable processor architecture) processor is a 32 bit RISC

architecture developed by Sun Microsystems for their workstations but

manufactured by a number of manufacturers such as LSI, Cypress, Fujitsu,

Philips and Texas Instruments.

The basic architecture follows the Berkeley model and uses register

windowing to improve context switching and parameter passing. The initial

designs were based on a discrete solution with separate floating point units,

memory management facilities and cache memory, but later designs have

integrated these versions. The latest versions also support superscalar

operation.

Architecture

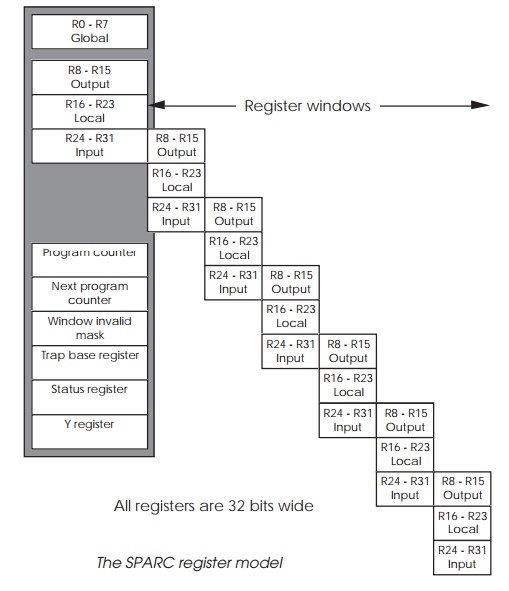

The SPARC system is based on the Berkeley RISC architecture. A large 32

bit wide register bank containing 120 registers is divided into a set of seven

register windows and a set of eight registers which are globally available.

Each window set contain-ing 24 registers is split into three sections to

provide eight input, eight local and eight output registers. The registers in

the output section provide the information to the eight input registers in the

next window. If a new window is selected during a context switch or as a

procedural call, data can be passed with no overhead by placing it in the

output registers of the first window. This data is then available for the

procedure or next context in its input registers. In this way, the windows are

linked together to form a chain where the input registers for one window have

the contents of the output registers of the previous window.

To return information back to the original or calling soft-ware, the

data is put into the input registers and the return executed. This moves the

current window pointer back to the previous window and the returned information

is now available in that window’s output registers. This method is the reverse

of that used to initially pass the information in the first place.

The programmer and CPU can track and control which windows are used and

what to do when all windows are full, through fields in the status register.

The architecture is also interesting in that it is one of the few RISC

processors that uses logical addressed caches instead of physically addressed

caches.

Interrupts

The SPARC processor supports 15 external interrupts which are generated

using the four interrupt lines, IRL0 – IRL3. Level 15 is assigned as a

non-maskable interrupt and the other 14 can be masked if required.

An external interrupt will generate an internal trap where the current

and the next instructions are saved, the pipeline flushed and the processor

switched into supervisor mode. The trap vector table which is located in the

trap base register is then used to supply the address of the service routine.

When the routine has completed, the REIT instruction is executed which restores

the processor status and allows it to continue.

Instruction set

The instruction set comprises of 64 instructions. All access to memory

is via load and store instructions as would be expected with a RISC architecture.

All other instructions operate on the register set including the currently

selected window. The instruc-tion set is also interesting in that it has a

multiply step command instead of the more normal multiply command. The multiply

step command allows a multiply to be synthesised.

Related Topics