Chapter: Embedded Systems Design : Memory systems

The MESI protocol

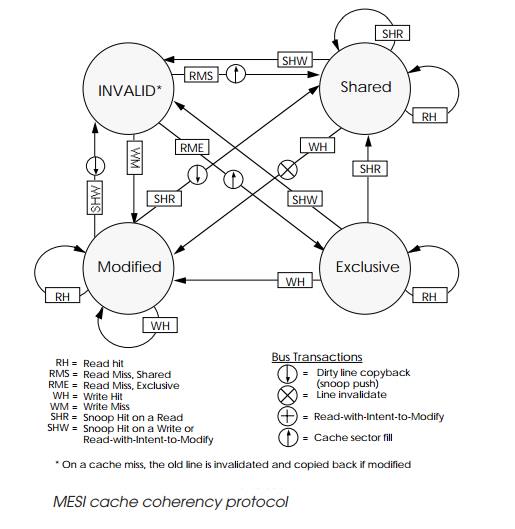

The MESI protocol

The MESI protocol is a formal mechanism for controlling cache coherency

using snooping techniques. Its acronym stands for modified, exclusive, shared,

invalid and refers to the states that cached data can take. Transition between

the states is controlled by memory accesses and bus snooping activity. This

information appears on special signal pins during bus transactions.

The MESI diagram is generic and shows the general opera-tion of the

protocol. There are four states that describe the cache contents and its

coherence with system memory:

Invalid The

target address is not cached.

Shared The target

address is in the cache and also in at

least one other. It is coherent with system memory.

Exclusive The target

address is in the cache but the data is coherent with system memory.

Modified The target

address is in the cache, but the contents has been modified and is not coherent

with system memory. No other cache in the system has this data.

The movement from one state is governed by memory actions, cache hits

and misses and snooping activity. For example, if a processor needs to write

data to a memory address that has a write-back policy and cache coherency

enabled as part of its page descriptors — controlled by the WIM bits — and

causes a cache miss, the processor will move from an invalid state to a

modified state by performing a ‘read with intent to modify’ bus cycle.

The MESI protocol is widely used in multiprocessor de-signs, for

example, in the Futurebus+ interconnection bus. The MPC601 uses this protocol.

Related Topics