Chapter: Embedded Systems Design : Memory systems

Big and little endian

Big and little endian

There are two methods of organising data within memory depending on where the most significant bit is located. The Intel 80x86 and Motorola 680x0 and PowerPC processors use different organisations and this can cause problems.

The PowerPC architecture uses primarily a big endian byte order, i.e. an address points to the most significant byte of a value in memory. This can cause problems with other processors that use the alternative little endian organisation, where an address points to the least significant byte.

The PowerPC architecture solves this problem by provid-ing a mode switch which causes all data memory references to be performed in a little-endian fashion. This is done by swapping address bit lines instead of using data multiplexers. As a result, the byte swapping is not quite what may be expected and varies depending on the size of the data. It is important to remember that swapping the address bits only reorders the bytes and not the individual bits within the bytes. The bit order remains constant.

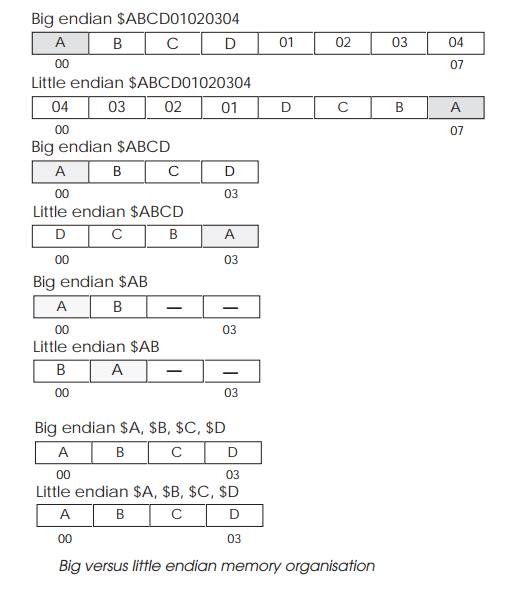

The diagram shows the different storage formats for big and little endian double words, words, half words and bytes. The most significant byte in each pair is shaded to highlight its posi-tion. Note that there is no difference when storing individual bytes.

An alternative solution for processors that do not imple-ment the mode swapping is to use the load and store instructions that byte reverse the data as it moves from the processor to the memory and vice versa.

Related Topics