Chapter: Embedded Systems Design : Basic peripherals

DMA implementations

DMA implementations

Intel 8237

This device is used in the IBM PC and is therefore probably the most

used DMA controller in current use. Like most peripher-als today, it has moved

from being a separate entity to be part of the PC chip set that has replaced

the 100 or so devices in the original design with a single chip.

It can support four main transfer modes including single and block

transfers, the demand mode and a special cascade mode where additional 8237 DMA

controllers can be cascaded to ex-pand the four channels that a single device

can support. It can transfer data between a peripheral and memory and by

combining two channels together, perform memory to memory transfers although

this is not used or supported within the IBM PC environ-ment. In addition,

there is a special verify transfer mode which is used within the PC to generate

dummy addresses to refresh the DRAM memory. This is done in conjunction with a

15 µs interrupt derived from a timer channel on the PC motherboard.

To resolve simultaneous DMA requests, there is an internal arbitration

scheme which supports either a fixed or rotating priority scheme.

Motorola MC68300 series

Whereas five or 10 years ago, DMA controllers were freely available as

separate devices, the increasing ability to integrate functionality has led to

their demise as separate entities and most DMA controllers are either

integrated onto the peripheral or as in this case onto the processor chip. The

MC68300 series combine an MC68000/MC68020 type of processor with peripherals

and DMA controllers.

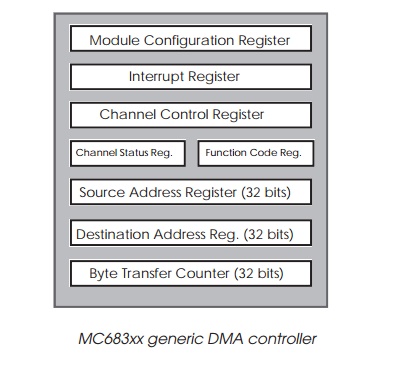

It consists of a two channel fully programmable DMA controller that can

support high speed data transfer rates of 12.5 Mbytes/s in dual address

transfer mode or 50 Mbytes/s in single address mode at a 25 MHz clock rate. The

dual address mode is considerably slower because two cycles have to be

performed as previously described. By virtue of its integration onto the

proces-sor chip with the peripherals and internal memory, it can DMA data

between internal and external resources. Internal cycles can be programmed to

occupy 25, 50, 75, or 100% of the available internal bus bandwidth while

external cycles support burst and single transfer mode.

The source and destination registers can be independently programmed to

remain constant or incremented as required.

Using another CPU with firmware

This is a technique that is sometimes used where a DMA controller is not

available or is simply not fast or sophisticated enough. The DMA CPU requires

its own local memory and program so that it can run in isolation and not burden

the main memory bus. The DMA CPU is sent messages which instruct it on how to

perform its DMA operations. The one advantage that this offers is that the CPU

can be programmed with higher level software which can be used to process the

data as well as transfer it. Many of the processors used in embedded systems

fall into this category of device.

Related Topics