Chapter: Embedded Systems Design : Basic peripherals

MC68230 modes

MC68230 modes

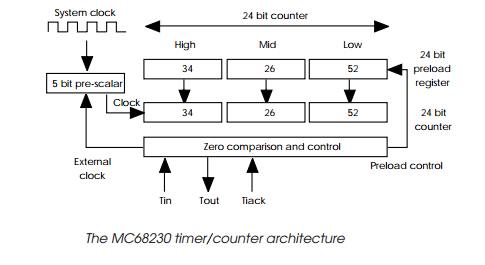

The Motorola MC68230 is a good example of a more pow-erful timer

architecture that can provide a far higher resolution than the Intel 8253. The

timer is based around a 24 bit architecture which is split into three 8 bit

components. The reason for this is that the device uses an 8 bit bus to

communicate with the host proces-sor such as a MC68000 CPU. This means that the

counter cannot be loaded directly from the processor in a single bus cycle. As

a result, three preload registers have been added to the basic architecture

previously described. These are preloaded using three separate accesses prior

to writing to the Z control bit in the control register. This transfers the

contents of the preload register to the counter as a single operation.

Instead of writing to the counter to either reset it or initialise it,

the host processor uses a combination of preload registers and the Z bit to

control the timer. The timer can be made to preload when it reaches zero or, as

an option, simply carry on counting. This gives a bit more flexibility in that

timing can be performed after the zero count as well as before it.

This architecture also has a 5 bit pre-scalar which is used to divide

the incoming clock which can be sourced from the system clock or externally via

the Tin signal. The pre-scalar can be loaded with any 5 bit value to divide the

clock before it drives the counter.

Related Topics