Chapter: Embedded Systems Design : Basic peripherals

DMA controller models

DMA controller models

There are various modes or models that DMA controllers can support ranging from simple to complex addressing modes and single and double data transfers.

Single address model

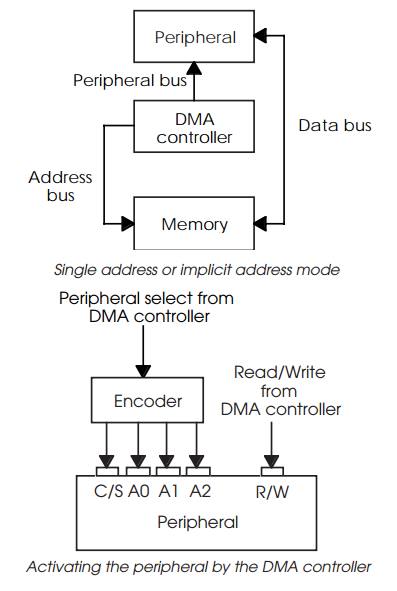

With the single address model, the DMA controller uses its address bus to address the memory location that will participate in the bus memory cycle. The controller uses a peripheral bus — in some cases a single select and a read/write pin — to select the peripheral device so its data bus becomes active. The select signal from the processor often has to generate an address to access the specific register within the peripheral such as the buffer register. If the peripheral is prompting the transfer, the peripheral would pull down a request line — typically its interrupt line is used for this purpose.

In this way, data can be transferred between the memory and peripheral as needed, without the data being transferred through the DMA controller and thus taking two cycles. This model is also known as the implicit address because the second address is implied and not directly given, i.e. there is no source address supplied.

Dual address model

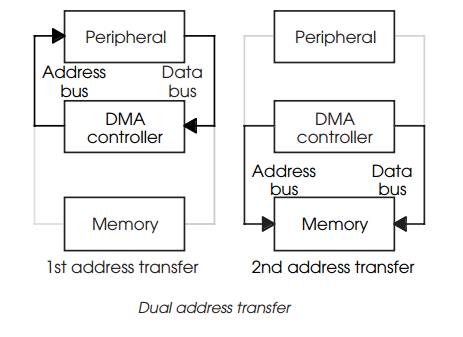

The dual address mode uses two addresses and two ac-cesses to transfer data between a peripheral or memory and another memory location. This consumes two bus cycles and uses a buffer within the DMA controller to temporarily hold data.

1D model

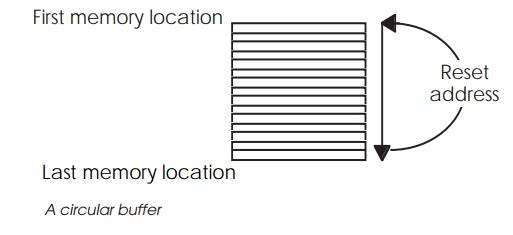

The 1D model uses an address location and a counter to define the sequence of addresses that are used during the DMA cycles. This effectively defines a block of memory which is used for the access. The disadvantage of this arrangement is that when the block is transferred, the address and counter are usually reset automatically and thus can potentially overwrite the previous data. This can be prevented by using an interrupt from the DMA controller to the processor when the counter has expired. This allows the CPU the opportunity to change the address so that next memory block to be used is different.

This model left on its own can be used to implement a circular buffer where the automatic reset is used to bring the address back to the beginning. Circular buffering can be an efficient technique in terms of both the size of buffering and timing constraints.

2D model

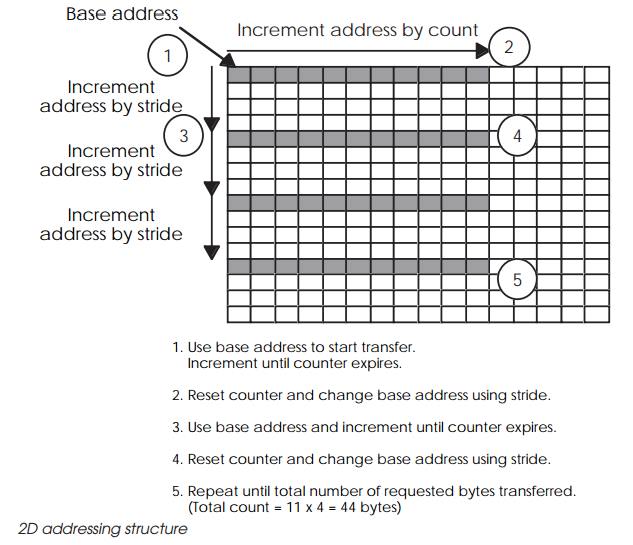

While the 1D model is simple, there are times especially with high speed data where the addressing mode is not powerful enough even though it can be augmented through processor intervention. A good example of this is with packet-based com-munication protocols where the data is wrapped up with addi-tional information in the form of headers. The packets typically have a maximum or fixed data format and thus large amounts of consecutive data have to be split and header and trailer informa-tion either added or removed.

With the 2D model, an address stride can be specified which is used to calculate an offset to the base address at the end of a count. This allows DMA to occur in non-consecutive blocks of memory. Instead of the base address being reset to the original address, it has the stride added to it. In addition the count register is normally split into two: one register to specify the count for the block and a second register to specify the total number of blocks or bytes to be transferred. Using these new features, it is easy to set up a DMA controller to transfer data and split into blocks ready for the insertion of header information. The diagram shows how this can be done.

3D model

The third type of controller takes the idea of address strides a step further by defining the ability to change the stride automati-cally so that blocks of different sizes and strides can be created. It is possible to simulate this with a 2D controller and software so that the processor reprograms the device to simulate the auto-matic change of stride.

Related Topics