Chapter: Microprocessor and Microcontroller

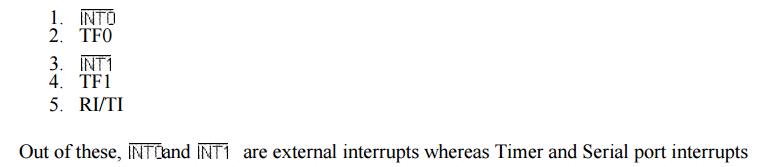

8051 interrupts

Interrupts

8051

provides 5 vectored interrupts. They are

are

external interrupts whereas Timer and Serial port interrupts are generated

internally. The external interrupts could be negative edge triggered or low

level triggered. All these interrupt, when activated, set the corresponding

interrupt flags. Except for serial interrupt, the interrupt flags are cleared

when the processor branches to the Interrupt Service Routine (ISR). The external

interrupt flags are cleared on branching to Interrupt Service Routine (ISR),

provided the interrupt is negative edge triggered. For low level triggered

external interrupt as well as for serial interrupt, the corresponding flags

have to be cleared by software by the programmer.

The

schematic representation of the interrupts is as follows -

Interrupt

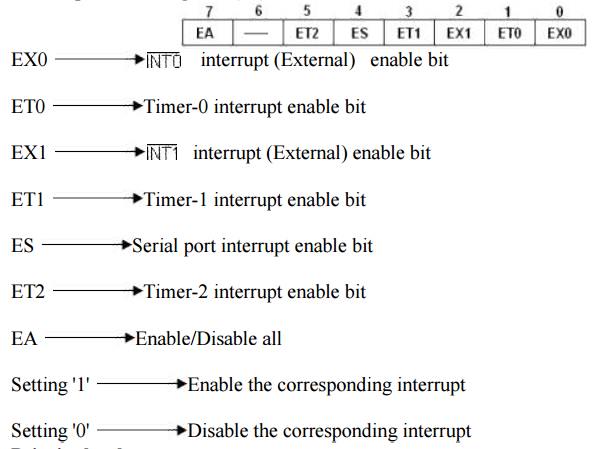

Each of

these interrupts can be individually enabled or disabled by 'setting' or

'clearing' the corresponding bit in the IE (Interrupt Enable Register) SFR. IE

contains a global enable bit EA which enables/disables all interrupts at once.

Interrupt Enable register (IE): Address:

A8H

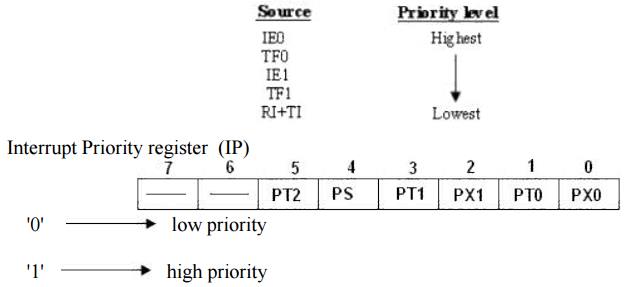

Priority level structure:

Each

interrupt source can be programmed to have one of the two priority levels by

setting (high priority) or clearing (low priority) a bit in the IP (Interrupt

Priority) Register . A low priority interrupt can itself be interrupted by a

high priority interrupt, but not by another low priority interrupt. If two

interrupts of different priority levels are received simultaneously, the

request of higher priority level is served. If the requests of the same

priority level are received simultaneously, an internal polling sequence

determines which request is to be serviced. Thus, within each priority level,

there is a second priority level determined by the polling sequence, as

follows.

Interrupt handling:

The

interrupt flags are sampled at P2 of S5 of every instruction cycle (Note that

every instruction cycle has six states each consisting of P1 and P2 pulses).

The samples are polled during the next machine cycle (or instruction cycle). If

one of the flags was set at S5P2 of the preceding instruction cycle, the

polling detects it and the interrupt process generates a long call (LCALL) to

the appropriate vector location of the interrupt. The LCALL is generated

provided this hardware generated LCALL is not blocked by any one of the

following conditions.

1. An

interrupt of equal or higher priority level is already in progress.

2. The

current polling cycle is not the final cycle in the execution of the

instruction in progress.

3. The

instruction in progress is RETI or any write to IE or IP registers.

When an

interrupt comes and the program is directed to the interrupt vector address,

the Program Counter (PC) value of the interrupted program is stored (pushed) on

the stack. The required Interrupt Service Routine (ISR) is executed. At the end

of the ISR, the instruction RETI returns the value of the PC from the stack and

the originally interrupted program is resumed.

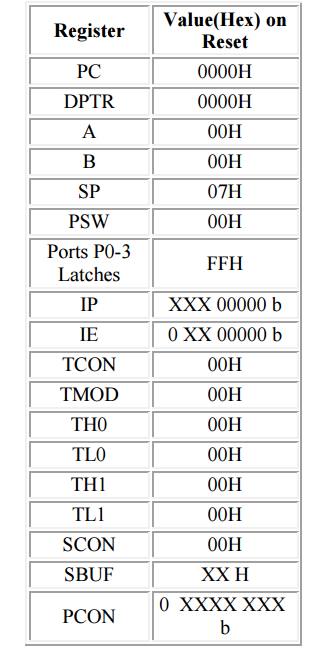

Reset is a non-maskable interrupt. A

reset is accomplished by holding the RST pin high for at least two machine cycles. On resetting the program starts from

0000H and some flags are modified as follows –

The

schematic diagram of the detection and processing of interrupts is given as

follows.

It should

be noted that the interrupt which is blocked due to the three conditions

mentioned before is not remembered unless the flag that generated interrupt is

not still active when the above blocking conditions are removed, i.e. ,every

polling cycle is new.

Jump and Call Instructions

There are

3 types of jump instructions. They are:-

1. Relative

Jump

2. Short

Absolute Jump

3. Long

Absolute Jump

Relative Jump

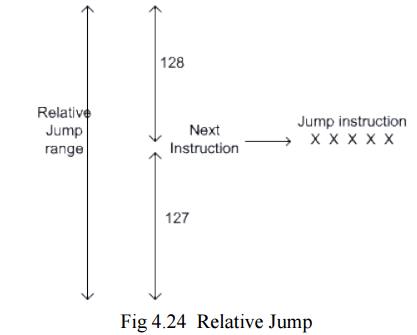

Jump that

replaces the PC (program counter) content with a new address that is greater

than (the address following the jump instruction by 127 or less) or less than

(the address following the jump by 128 or less) is called a relative jump.

Schematically, the relative jump can be shown as follows: -

The

advantages of the relative jump are as follows:-

Only 1

byte of jump address needs to be specified in the 2's complement form, ie. For

jumping ahead, the range is 0 to 127 and for jumping back, the range is –

1 to

-128.

2. Specifying

only one byte reduces the size of the instruction and speeds up program

execution.

3. The

program with relative jumps can be relocated without reassembling to generate

absolute jump addresses.

Disadvantages

of the absolute jump: -

1. Short

jump range (-128 to 127 from the instruction following the jump instruction)

Instructions

that use Relative Jump

SJMP

<relative address>

(The

remaining relative jumps are conditional jumps)

JC

<relative address> JNC <relative address> JB bit, <relative

address> JNB bit, <relative address> JBC bit, <relative address>

CJNE

<destination byte>, <source byte>, <relative address> DJNZ

<byte>, <relative address>

JZ

<relative address> JNZ <relative address>

Short Absolute Jump

In this

case only 11bits of the absolute jump address are needed. The absolute jump

address is calculated in the following manner.

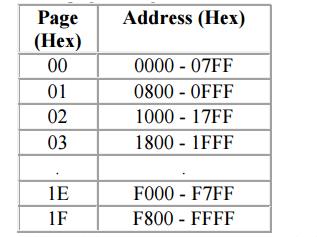

In 8051,

64 kbyte of program memory space is divided into 32 pages of 2 kbyte each. The

hexadecimal addresses of the pages are given as follows:-

It can be

seen that the upper 5bits of the program counter(PC) hold the page number and

the lower 11bits of the PC hold the address within that page. Thus, an absolute

address is formed by taking page numbers of the instruction (from the program

counter) following the jump and attaching the specified 11bits to it to form

the 16-bit address.

Advantage:

The instruction length becomes 2 bytes.

However,

difficulty is encountered when the next instruction following the jump

instruction begins from a fresh page (at X000H or at X800H). This does not give

any

problem

for the forward jump, but results in an error for the backward jump. In such a

case the assembler prompts the user to relocate the program suitably.

Example

of short absolute jump: - ACALL <address 11>

AJMP <address 11>

Long Absolute Jump/Call

Applications

that need to access the entire program memory from 0000H to FFFFH use long

absolute jump. Since the absolute address has to be specified in the op-code,

the instruction length is 3 bytes (except for JMP @ A+DPTR). This jump is not

re-locatable.

Example:

-

LCALL

<address 16>

LJMP <address 16>

JMP

@A+DPTR

Related Topics