Chapter: Basic Electrical and electronics : Digital Electronics

Important Short Question and Answers: Digital Electronics

DIGITAL ELECTRONICS

1) Given

the two binary numbers X = 1010100 and Y = 1000011, perform the subtraction (a)

X -Y and (b) Y - X using 2's complements.

There is

no end carry,

Therefore

the answer is Y-X = -(2's complement of 1101111) = -0010001

2). Given the two binary numbers X = 1010100

and Y = 1000011, perform the subtraction

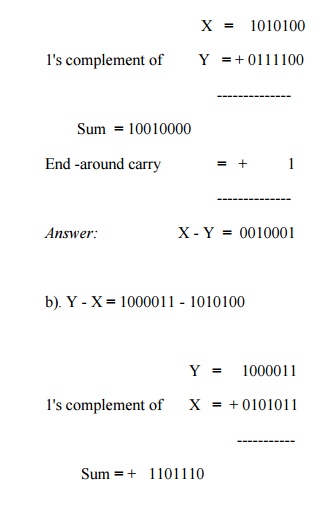

(a) X -Y and (b) Y - X using 1's complements.

a). X -

Y = 1010100 - 1000011

There is

no end carry.

Therefore

the answer is Y - X = -(1's complement of 1101110) = -0010001

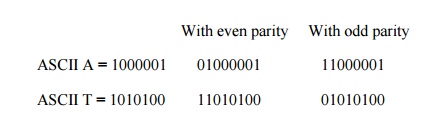

3). What is meant by parity bit?

A parity

bit is an extra bit included with a message to make the total number of 1's

either even or odd. Consider the following two characters and their even and

odd parity:

In each

case we add an extra bit in the left most position of the code to produce an

even number of 1's in the character for even parity or an odd number of 1's in

the character for odd parity. The parity bit is helpful in detecting errors

during the transmission of information from one location to another.

4).Define binary logic?

Binary logic consists of binary variables and logical operations.

The variables are designated by the alphabets such as A, B, C, x, y, z, etc.,

with each variable having only two distinct values: 1 and 0. There are three

basic logic operations: AND, OR, and NOT.

5).Define logic gates?

Logic gates are electronic circuits that operate on one or more

input signals to produce an output signal. Electrical signals such as voltages

or currents exist throughout a digital system in either of two recognizable

values. Voltage- operated circuits respond to two separate voltage levels that

represent a binary variable equal to logic 1 or logic 0.

6).Define duality property.

Duality property states that every algebraic expression deducible

from the postulates of Boolean algebra remains valid if the operators and

identity elements are interchanged. If the dual of an algebraic expression is

desired, we simply interchange OR and AND operators and replace 1's by 0's and

0's by 1's.

7).Find the complement of the functions F1

= x'yz' + x'y'z and F2 = x(y'z' + yz). By applying De Morgan's

theorem as many times as necessary.

F1' = (x'yz' + x'y'z)' = (x'yz')'(x'y'z)' = (x

+ y' + z)(x + y +z')

F2' = [x(y'z' + yz)]' = x' + (y'z' + yz)'

= x' + (y'z')'(yz)'

= x' + (y + z)(y' + z')

8).Find the complements of the functions F1 =

x'yz' + x'y'z and F2 = x(y'z' + yz). by taking their duals and complementing

each literal.

F1 = x'yz' + x'y'z

The dual

of F1 is (x' + y + z')(x' + y' + z)

Complementing

each literal: (x + y' + z)(x + y + z')

F2 = x(y'z' + yz).

The dual

of F2 is x + (y' + z')(y + z).

Complement

of each literal: x' + (y + z)(y' + z')

9).State De Morgan's theorem.

De Morgan suggested two theorems that form

important part of Boolean algebra. They are,

1) The complement of a

product is equal to the sum of the complements. (AB)' = A' + B'

2) The complement of a sum

term is equal to the product of the complements. (A + B)' = A'B'

10).Reduce A.A'C

A.A'C = 0.c [A.A' = 1]

= 0

11). Reduce A(A + B)

A(A + B)

= AA + AB

= A(1 + B) [1 + B = 1]

= A.

12.

Reduce A'B'C' + A'BC' + A'BC

A'B'C' +

A'BC' + A'BC = A'C'(B' + B) + A'B'C

= A'C' + A'BC [A + A' = 1]

= A'(C' + BC)

= A'(C' + B) [A + A'B = A + B]

13.) Reduce AB + (AC)' + AB'C(AB + C)

AB +

(AC)' + AB'C(AB + C) = AB + (AC)' + AAB'BC + AB'CC

= AB + (AC)' + AB'CC [A.A' = 0]

= AB + (AC)' + AB'C [A.A = 1]

= AB + A' + C' =AB'C [(AB)' = A' + B']

= A' + B + C' + AB'C [A + AB' = A + B]

= A' + B'C + B + C' [A + A'B = A + B]

= A' + B + C' + B'C

=A' + B + C' + B'

=A' + C' + 1

= 1 [A

+ 1 =1]

14. Simplify the following expression Y = (A +

B)(A + C' )(B' + C' )

Y = (A + B)(A + C' )(B' + C' )

= (AA' + AC +A'B +BC )(B' +

C') [A.A' = 0]

= (AC + A'B + BC)(B' + C' )

= AB'C + ACC' + A'BB' + A'BC' + BB'C + BCC'

= AB'C + A'BC'

15).Simplify the following using De Morgan's

theorem [((AB)'C)'' D]'

[((AB)'C)'' D]' = ((AB)'C)'' +

D' [(AB)'

= A' + B']

= (AB)' C + D'

= (A' + B' )C + D'

16.Show that (X + Y' + XY)( X + Y')(X'Y) = 0

(X + Y'

+ XY)( X + Y')(X'Y) = (X + Y' + X)(X + Y' )(X' + Y) [A + A'B = A + B]

= (X + Y' )(X + Y' )(X'Y) [A + A = 1]

= (X + Y' )(X'Y) [A.A = 1]

= X.X' + Y'.X'.Y

= 0 [A.A'

= 0]

17).Prove that ABC + ABC' + AB'C + A'BC = AB +

AC + BC

ABC + ABC' + AB'C + A'BC =AB(C + C') + AB'C +

A'BC

=AB + AB'C + A'BC

=A(B + B'C) + A'BC

=A(B + C) + A'BC

=AB + AC + A'BC

=B(A + C) + AC

=AB + BC + AC

=AB + AC +BC ...Proved

18).Convert the given expression in canonical

SOP form Y = AC + AB + BC

Y = AC + AB + BC

=AC(B + B' ) + AB(C + C' ) + (A + A')BC

=ABC + ABC' + AB'C + AB'C' + ABC + ABC' + ABC

=ABC + ABC' +AB'C + AB'C' [A + A =1]

19).Convert the given expression in canonical

POS form Y = ( A + B)(B + C)(A + C)

Y = ( A + B)(B + C)(A + C)

= (A + B + C.C' )(B + C + A.A' )(A + B.B' + C)

= (A + B + C)(A + B + C' )(A + B +C)(A' + B +C)(A

+ B + C)(A + B' + C)

[A + BC = (A + B)(A + C) (Distributive law]

= (A + B + C)(A + B + C')(A' + B + C)(A' + B +

C)(A + B' + C)

20)

Write

down the steps in implementing a Boolean function with levels of NAND Gates?

Simplify the function and express it in sum of

products.

Draw a NAND gate for each product term of the

expression that has at least two literals.

The

inputs to each NAND gate are the literals of the term. This constitutes a group

of first level gates. Draw a single gate using the AND-invert or the invert-OR

graphic symbol in the second level, with inputs coming from outputs of first

level gates.

A term with a single literal requires an inverter in the first

level. How ever if the single literal is complemented, it can be connected

directly to an input of the second level NAND gate.

21) Give the general procedure for converting a

Boolean expression in to multilevel NAND diagram?

Draw the AND-OR diagram of the Boolean

expression.

Convert all AND gates to NAND gates with

AND-invert graphic symbols. Convert all OR gates to NAND gates with invert-OR

graphic symbols.

Check all the bubbles in the same diagram. For

every bubble that is not compensated by another circle along the same line,

insert an inverter or complement the input literal.

22) What are combinational circuits?

A combinational circuit consists of logic gates whose outputs at

any time are determined from the present combination of inputs. A combinational

circuit performs an operation that can be specified logically by a set of

Boolean functions. It consists of input variables, logic gates, and output

variables.

23) Give the design procedures for the

designing of a combinational circuit.

The procedure involves the following steps,

From the specification of the circuit,

determine the required number of inputs and outputs and assign a symbol to

each.

Derive the truth table that defines the

required relationships between inputs and outputs. Obtain the simplified

Boolean functions for each output as a function of the input variables.

Draw the logic diagram and verify the

correctness of the design.

24) Define half adder.

A combinational circuit that performs the addition of two bits is

called a half adder. A half adder needs two binary inputs and two binary

outputs. The input variables designate the augend and addend bits; the output

variables produce the sum and carry

25) Define full adder?

A combinational circuit that performs the adtion of three bits is a

full adder.It consists of three inputs and two outputs.

The carry into sign bit position and the carry out of the sign bit

position. If these two carries are not equal, an overflow has occurred.

26.

Represent binary number 1101 - 101 in power of

2 and find its decimal equivalent

N = 1 x 2 3 + 1 x 2 2 + 0 x 2 1 + 1 x 2 0 + 1 x

2 -1 + 0 x 2 -2 + 1 x 2 -3

= 13.625 10

27.

What are the different classification of binary

codes?

1. Weighted codes

2. Non - weighted codes

3. Reflective codes

. Sequential codes

5. Alphanumeric codes

6. Error Detecting and correcting codes.

28.

Write the names of basic logical operators.

1. NOT / INVERT

2. AND

3. OR

29.

Simplify the following expression y = (A + B) (A = C) (B + C)

= (A A + A C + A B + B C) (B + C) = (A C + A B

+ B C) (B + C)

= A B C + A C C + A B B + A B C + B B C + B C C

= A B C = A B C

30.

Show that the NAND connection is not

associative

The NAND connection is not associative says

that A . B . C A . B. C

A . B + C A + B C AB + C A + BC

31.

What is a Logic gate?

Logic gates are the basic elements that make up

a digital system. The electronic gate is a circuit that is able to operate on a

number of binary inputs in order to perform a particular logical function.

32.

Write the names of Universal gates.

1. NAND gate

2. NOR gate

33. Why are NAND and NOR gates known as

universal gates?

The NAND and NOR gates are known as universal

gates, since any logic function can be implemented using NAND or NOR gates.

34. Define combinational logic

When logic gates are connected together to

produce a specified output for certain specified combinations of input variables,

with no storage involved, the resulting circuit is called combinational logic.

35.

Explain the design procedure for combinational

circuits

¢ The problem definition

¢ The determination of number of available input

variables & required O/P variables.

¢ Assigning letter symbols to I/O variables

¢ Obtain simplified boolean expression for each

O/P.

¢ Obtain the logic diagram.

36.

Define half adder and full adder

The logic circuit which performs the addition

of two bits is a half adder.

The circuit which performs the addition of

three bits is a full adder.

Related Topics