Chapter: VLSI Design : Specification Using Verilog HDL

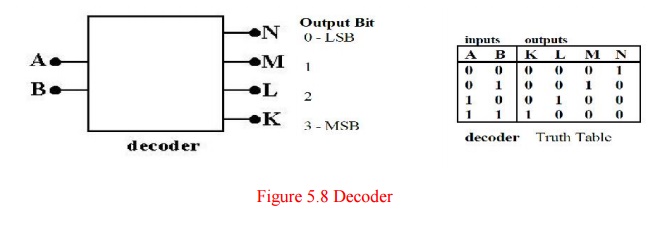

Structural Gate Level Description of Decoder

STRUCTURAL GATE LEVEL DESCRIPTION

OF DECODER

1. DECODER

module

mux (sel, res);

input [2:0] sel;

output

[7:0] res;

reg [7:0] res;

always

@(sel or res)

begin

case

(sel)

3’b000 :

res = 8’b00000001;

3’b001 :

res = 8’b00000010;

3’b010 :

res = 8’b00000100;

3’b011 :

res = 8’b00001000;

3’b100 :

res = 8’b00010000;

3’b101 :

res = 8’b00100000;

3’b110 :

res = 8’b01000000;

default :

res = 8’b10000000;

endcase

end

endmodule

2. EQUALITY DETECTOR

3. Comparator

module

compar(a, b, cmp);

input

[7:0] a;

input

[7:0] b;

output

cmp;

assign

cmp = (a >= b) ? 1’b1 : 1’b0;

endmodule

4. Priority Encoder.

module

priority (sel, code);

input [7:0] sel;

output

[2:0] code;

reg [2:0] code;

always

@(sel)

begin

if

(sel[0])

code =

3’b000;

else if

(sel[1]) code = 3’b001;

else if

(sel[2]) code = 3’b010;

else if

(sel[3]) code = 3’b011;

else if

(sel[4]) code = 3’b100;

else if

(sel[5]) code = 3’b101;

else if

(sel[6]) code = 3’b110;

else if

(sel[7]) code = 3’b111;

else

code =

3’bxxx;

end

endmodule

5. HALF ADDER module ha(s,cy,a,b);

input

a,b;

output

s,cy;

assign

s=(a ^ b);

assign

cy=(a & b);

endmodule

6. FULL ADDER

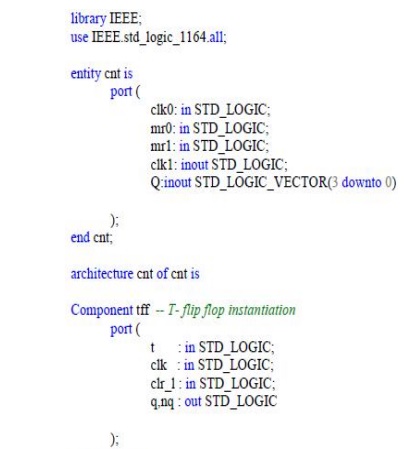

Program:

library

ieee;

use

ieee.std_logic_1164.all;

entity

full is

port(a,b,c:in

std_logic;

sum,

carry:out std_logic);

end full;

architecture

behave of full is

begin

sum <=

a xor b xor c;

carry

<= (a and b) or (b and c) or (c and a);

end

behave;

7. Ripple carry adder module adder(a, b, sum, co);

input

[7:0] a; input [7:0] b; output [7:0] sum; output co; wire [8:0] tmp;

assign

tmp = a + b; assign sum = tmp [7:0]; assign co = tmp [8];

endmodule

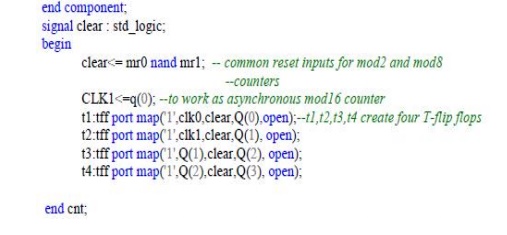

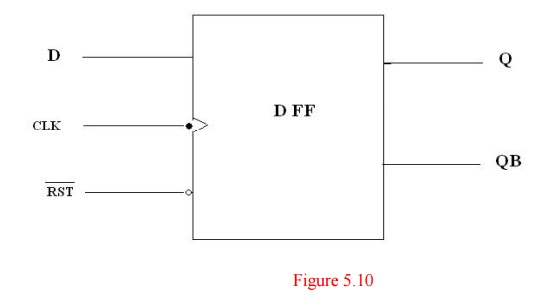

8. D-LATCH

9. D-FLIP FLOP

module

dff(q,d,rst,clk); input d,rst,clk; output q;

reg q;

always@(posedge

rst or negedge clk) if (rst)

q=1'b0;

else q=d;

endmodule

Related Topics