Chapter: VLSI Design : Specification Using Verilog HDL

Operators - Verilog HDL

OPERATORS

Verilog

has large number of operators.

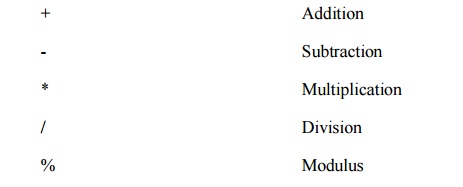

1. Binary Arithmetic

Operators

Binary

arithmetic operators operate on two operands. Register and net (wire) operands

are treated as unsigned. However, real and integer operands may be signed. If

any bit is unknown ('x') then result

is unknown.

2. Operator Name

3. Relational Operators

Relational

operators compare two operands and return a logical value, i. e., TRUE(1) or

FALSE(0). If any bit is unknown, the relation is ambiguous and the result is

unknown.

Operator Name

> Greater than

>= Greater than or equal

< Less than

<= Less than or equal

== Logical equality

!= Logical inequality

4. Logical Operators

Logical

operators operate on logical operands and return a logical value, i. e.,

TRUE(1) or FALSE(0). Used typically in if

and while statements. Do not confuse

logical operators with the bitwise Boolean operators. For example , ! is a

logical NOT and ~ is a bitwise NOT. The first negates, e. g., !(5 == 6) is

TRUE. The second complements the bits, e. g., ~{1,0,1,1} is 0100.

5. Bitwise Operators

Operator Name

! Logical negation

&& Logical AND

|| Logical OR

Bitwise

operators operate on the bits of the operand or operands. For example, the

result of A & B is the AND of each corresponding bit of A with B. Operating

on an unknown (x) bit results in the

expected value. For example, the AND of an x

with a FALSE is an x. The OR of an x with a TRUE is a TRUE.

Operator Name

~ Bitwise negation

& Bitwise AND

| Bitwise OR

^ Bitwise XOR

~& Bitwise NAND

~| Bitwise NOR

6. Unary Reduction

Operators

Unary

reduction operators produce a single bit result from applying the operator to

all of the bits of the operand. For example, &A will AND all the

bits of A.

7. Unary Arithmetic

Operators

Operator : Name : Comments

- : Unary Minus : Changes sign of its operand.

Related Topics