Chapter: Microprocessor and Microcontroller : 8086 System Bus Structure

Important Short Questions and Answers: Microprocessor and Microcontroller - 8086 System Bus Structure

SYSTEM BUS STRUCTURE

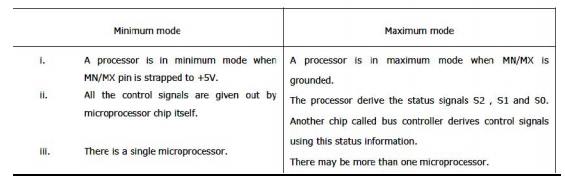

1. Differentiate between minimum and maximum mode

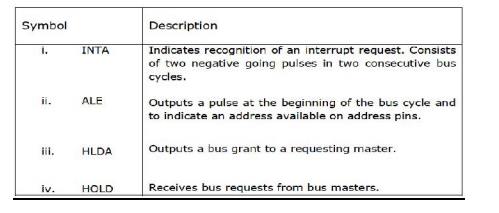

2. Give any four pin definitions for the minimum

mode.

3. What are the pins that are used to indicate

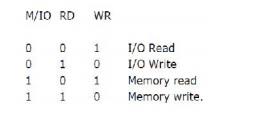

the type of transfer in minimum mode?

The M/IO,

RD, WR lines specify the type of transfer. It is indicated in the following

table:

4. What

are the functional parts of 8086 CPU?

The two

independent functional parts of the 8086 CPU are: i. Bus Interface Unit (BIU):

BIU sends

out addresses, fetches instruction from memory, reads data from ports and

memory and writes data to ports and memory.

ii.

Execution Unit (EU):

EU tells

the BIU where to fetch instructions or data, decodes instructions and executes

instructions.

5. What

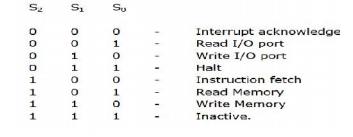

is the operation of S0, S1 and S2 pins in maximum mode?

S2, S1,

S0 indicates the type of transfer to take place during the current bus cycle.

6. Give

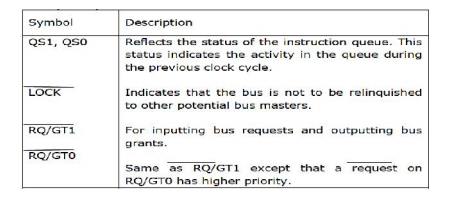

any four pin definitions for maximum mode.

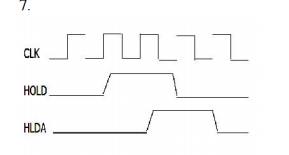

7. Draw

the bus request and bus grant timings in minimum mode system.

8. What

is the purpose of a decoder in EU?

The

decoder in EU translates instructions fetched from memory into a series of

actions, which the EU carries out.

9. Give the

register classification of 8086. The 8086 contains:

i.

General purpose registers: They are used for holding data, variables and

intermediate results temporarily.

ii.

Special purpose registers: They are used as segment registers, pointers, index

register or as offset storage registers for particular addressing modes.

10.

What are general data registers?

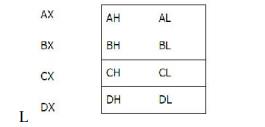

The

registers AX,BX,CX and DX are the general data registers.

L and H

represents the lower and higher bytes of particular register. AX register is

used as 16-bit accumulator.

BX

register is used as offset storage for forming physical addresses in case of

certain addressing modes.

CX

register is used as a default counter in case of string and loop instructions.

DX

register is used as an implicit operand or destination in case of a few

instructions.

11.

Give the different segment registers. The four

segment registers are:

i. Code

segment register: It is used for addressing a memory location in the code

segment of the memory, where the executable program is stored.

ii. Data

segment register: It points to the data segment of the memory, where data is

resided. iii. Extra segment register: It also contains data.

iv. Stack

segment register: It is used for addressing stock segment of memory. It is used

to store stack data.

12.

What are pointers and index registers?

IP, BP and

SP are the pointers and contain offsets within the code, data and stack

segments respectively. SI and DI are the index registers, which are used as

general purpose registers

and also

for offset storage in case of indexed, based indexed and relative based indexed

addressing modes.

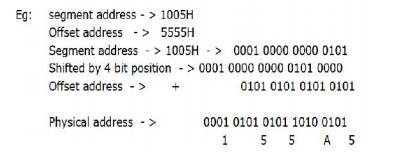

13.How is

the physical address calculated? Give an example.

The

physical address, which is 20-bits long is calculated using the segment and

offset registers, each 16-bits long. The segment address is shifted left

bit-wise four times and offset address is added to this to produce a 20 bit

physical address.

14. What

is meant by memory segmentation?

Memory

segmentation is the process of completely dividing the physically available

memory into a number of logical segments. Each segment is 64K byte in size and

is addressed by one of the segment register.

15. What

are the advantages of segmented memory? The advantages of segmented memory are:

i. Allows

the memory capacity to be 1Mbyte, although the actual addresses to be handled

are of 16-bit size.

ii. Allows

the placing of code, data and stack portions of the same program in different

parts of memory for data and code protection.

iii. Permits a

program and/or its data to be put into different areas of memory, each times

program is executed i.e., provision for relocation may be done.

16. What

is pipelining?

Fetching

the next instruction while the current instruction executes is called

pipelining

17. What

are the two parts of a flag register? The two parts of the 16 bit flag register

are: i. Condition code or status flag register:

It

consists of six flags to indicate some condition produced by an instruction.

ii. Machine control flag register:

It

consists of three flags and are used to control certain operations of the processor

18.Draw

the format of 8086 flag register. 8086 flag register:

19.

Explain the three machine control flags. i. Trap flag:

If this

flag is set, the processor enters the single step execution.

ii.

Interrupt flag: If this flag is set, the markable interrupts are recognized by

the CPU,

otherwise

they are ignored.

iii.

Direction flag: This is used by string manipulation instructions. If this flag

bit is „0‟,the string is processed from the lowest to the highest address i.e.,

auto incrementing mode. Otherwise, the string is processed from highest address

to lowest address, i.e., auto decrementing mode.

20. What

are the three groups of signals in 8086? The 8086 signals are categorized in

three groups. They are:

i. The

signals having common functions in minimum and maximum mode. ii. The signals

having special functions for minimum mode.

iii. The

signals having special functions for maximum mode.

21. What

are the uses of AD15 – AD0 lines?

AD15 –

AD0 are time multiplexed memory I/O address and data lines. Address remains on

the lines during T1 state, while data is available on data bus during T2, T3,

Tw and T4 states. These lines are active high and float to a tristate during

interrupt acknowledge and local bus hold acknowledge cycles.

22. What

is the operation of RD signal?

RD is an

active low signal. When it is low, it indicates the peripherals that the

processor is performing a memory or I/O read operation.

23.Give

the function of i. Ready and ii. INTR signal.

i. Ready

signal: It is an acknowledgement from slow devices of memory that they have

completed data transfer. The signal is synchronized by 8284 A clock generator

to give ready input to 8086. The signal is active high.

INTR

signal: It is a level triggered input. This is sampled during the last cycle of

each instruction to determine the availability of the request. If any interrupt

request is pending, the processor enters the interrupt acknowledge cycle. This

can be internally masked by resetting the interrupt enable flag. The signal is

active high and internally synchronized.

24. What

is the operation performed when TEST input is low?

When the

TEST input is low, execution will continue, else, the processor remains in an

idle state.

25. What

is NMI (Non-Maskable Interrupt)?

NMI is an

edge-triggered input, which causes a type 2 interrupt. It is not maskable internally

by software and transition from low to high initiate the interrupt response at

the end of the current instruction. This input is internally synchronized.

22. What

is the purpose of clock input?

The clock

input provides the basic timing for processor operation and bus control

activity. It is an asymmetric square wave with 33% duty cycle. The range of

frequency varies from 5MHz to 10MHz.

23. What

is the function of MN/MX pin?

The logic

level at MN/MX pin decides whether processor operates in minimum or maximum

mode.

24. What

happens when a high is applied to RESET pin?

When a

high is given to RESET pin, the processor terminates the current activity and

starts executing from FFFF0H. It must be active for at least four clock cycles.

It is internally synchronized.

25.

What will happen when a DMA request is made, while

the CPU is performing a memory or I/O cycles?

When a

DMA request is made, while the CPU is performing a memory or I/O cycles, it

will request the local bus during T4 provided:

i. The request

occurs on or before T2 state of the current cycle.

ii. The

current cycle is not operating over the lower byte of a word.

iii. The

current cycle is not the first acknowledge of an interrupt acknowledge

sequence. iv. A lock instruction is not being executed.

26.

What is multiprogramming?

If more

than one process is carried out at the same time, then it is know as

multiprogramming. Another definition is the interleaving of CPU and I/O

operations among several programs is called multiprogramming. To improve the

utilization of CPU and I/O devices, we are designing to process a set of

independent programs concurrently by a single CPU. This technique is known as

multiprogramming

27.

Write the advantages of loosely coupled system over

tightly coupled systems?

1. More number of CPUs can be added in a loosely coupled system to improve the system performance

2. The system structure is modular and hence easy to maintain and troubleshoot.

3. A fault

in a single module does not lead to a complete system breakdown.

28.

What is the different clock frequencies used in

80286?

Various

versions of 80286 are available that run on 12.5MHz, 10MHz and 8MHz clock

frequencies.

29.

Define swapping in?

The

portion of a program is required for execution by the CPU, it is fetched from

the secondary memory and placed in the physical memory. This is called

‘swapping in’ of the program.

30 What

are the different operating modes used in 80286? The 80286 works in two

operating modes

1. Real

addressing mode

2.

Protected virtual address mode.

31. What

are the CPU contents used in 80286?

The 80286

CPU contains almost the same set of registers, as in 8086

• Eight

16-bit general purpose register

• Four

16-bit segment registers

• Status

and control register

• Instruction pointer.

Related Topics