Chapter: Embedded Systems Design : Interrupts and exceptions

The interrupt mechanism

The interrupt mechanism

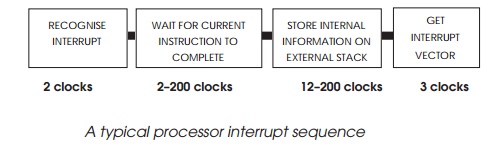

Once an interrupt or exception has been recognised, then the processor

goes through an internal sequence to switch the processing thread and activate

the ISR or exception handler that will service the interrupt or exception. The

actual process and, more importantly, the implied work that the service routine

must perform varies from processor architecture to architecture. The general

processing for an MC68000 or 80x86 which uses a stack frame to hold essential

data is different from a RISC processor that uses special internal registers.

Before describing in detail some of the most used mecha-nisms, let’s

start with a generic explanation of what is involved. The first part of the

sequence is the recognition of the interrupt or exception. This in itself does

not necessarily immediately trigger any processor reaction. If the interrupt is

not an error condition or the error condition is not connected with the

currently executing instruction, the interrupt will not be internally processed

until the currently executing instruction has completed. At this point, known

as an instruction boundary, the processor will start to internally process the

interrupt. If, on the other hand, the interrupt is due to an error with the

currently executing instruction, the instruction will be aborted to reach the

instruction boundary.

At the instruction boundary, the processor must now save certain state

information to allow it to continue its previous execution path prior to the

interrupt. This will typically include a copy of the condition code register,

the program counter and the return address. This information may be extended to

include internal state information as well. The register set is not normally

included.

The next phase is to get the location of the ISR to service the

interrupt. This is normally kept in a vector table somewhere in memory and the

appropriate vector can be supplied by the periph-eral or preassigned, or a

combination of both approaches. Once the vector has been identified, the

processor starts to execute the code within the ISR until it reaches a return

from interrupt type of instruction. At this point, the processor, reloads the

status infor-mation and processing continues the previous instruction stream.

Stack-based processors

With stack-based processors, such as the Intel 80x86, Motorola M68000

family and most 8 bit microcontrollers based on the original microprocessor

architectures such as the 8080 and MC6800, the context information that the

processor needs to preserve is saved on the external stack.

When the interrupt occurs, the processor context informa-tion such as

the return address, copies of the internal status registers and so on are

stored out on the stack in a stack frame. These stack frames can vary in size

and content depending on the source of the interrupt or exception.

When the interrupt processing is completed, the informa-tion is

extracted back from the stack and used to restore the processing prior to the

interrupt. It is possible to nest interrupts so that several stack frames and interrupt

routines must be executed prior to the program flow being restored. The number

of routines that can be nested in this way depends on the storage space

available. With external stacks, this depends in turn on the amount of

available memory.

Other processors use an internal hardware stack to reduce the external

memory cycles necessary to store the stack frame. These hardware stacks are

limited in the number of interrupts or exceptions that can be nested. It then

falls to the software designer to ensure that this limit is not exceeded. To

show these different interrupt techniques, let’s look at some processor

examples.

Related Topics