Chapter: VLSI Design : Circuit Characterization and Simulation

Delay Estimation

DELAY ESTIMATION

Estimation

of the delay of a Boolean function from its functional description is an

important step towards design exploration at the register transfer level (RTL).

This

addresses the problem of estimating the delay of certain optimal multi-level

implementations of combinational circuits, given only their functional

description.

The

proposed delay model uses a new complexity measure called the delay measure to

estimate the delay.

It has an

advantage that it can be used to predict both, the minimum delay (associated

with an optimum delay implementation) and the maximum delay (associated with an

optimum area implementation) of a Boolean function without actually resorting

to logic synthesisThe model is empirical and results demonstrating its

feasibility and utility are presented.

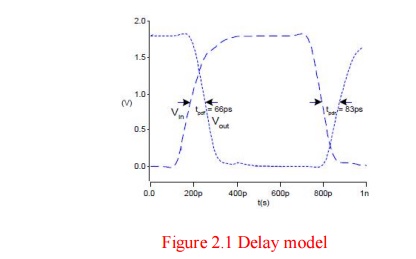

§ tpdr:

rising propagation delay

§ From

input to rising output crossing VDD/2

§ tpdf:

falling propagation delay

§ From

input to falling output crossing VDD/2

§ tpd:

average propagation delay tpd = (tpdr + tpdf)/2

§ tr:

rise time

§ From

output crossing 20% to 80% VDD

§ tf:

fall time

§ From

output crossing 80% to 20% VDD

§ tcd:

average contamination delay tcd = (tcdr + tcdf)/2

§ tcdr:

rising contamination delay: Min from input to rising output crossing VDD/2

tcdf:

§ falling

contamination delay: Min from input to falling output cross inVDD/2

Solving

differential equations by hand is hard. SPICE like simulators used for accurate

analysis. But simulations are expensive. We need to be able to estimate delay

although not as accurately as simulator.

§ Use RC

delay models to estimate delay

§ C = total

capacitance on the output node

§ Use

Effective resistance R Therefore tpd = RC

§ Transistors are characterized by finding their effective R.

Related Topics