Chapter: Computer Architecture : Memory and I/O Systems

TLBS- Input/Output System

TLBS- INPUT/OUTPUT

SYSTEM

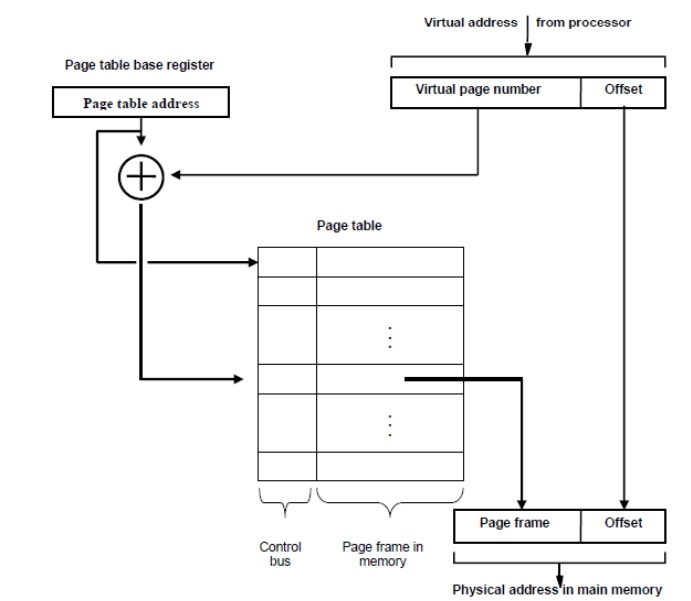

The MMU must use the

page table information for every read and write access; so ideally, the page

table should be situated within the MMU. Unfortunately, the page table may be

rather large, and since the MMU is normally implemented as part of the processor

chip (along with the primary cache), it is impossible to include a complete

page table on this chip. Therefore, the page table is kept in the main memory.

However, a copy of a small portion of the page table can be accommodated within

the MMU.

This portion consists

of the page table entries that correspond to the most recently accessed pages.

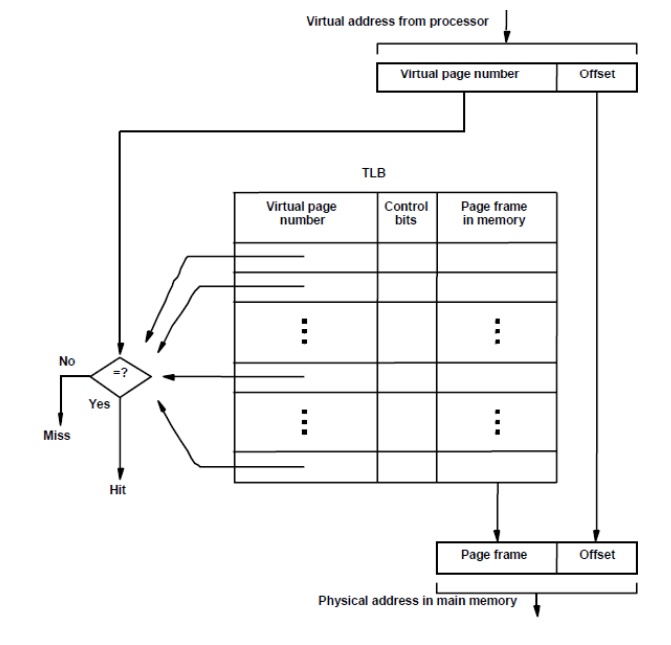

A small cache, usually called the Translation Lookaside Buffer (TLB) is

incorporated into the MMU for this purpose. The operation of the TLB with

respect to the page table in the main memory is essentially the same as the

operation of cache memory; the TLB must also include the virtual address of the

entry. Figure shows a possible organization of a TLB where the

associative-mapping technique is used. Setassociative mapped TLBs are also

found in commercial products.

An essential

requirement is that the contents of the TLB be coherent with the contents of

page tables in the memory. When the operating system changes the contents of

page tables, it must simultaneously invalidate the corresponding entries in the

TLB. One of the control bits in the TLB is provided for this purpose. When an

entry is invalidated, the TLB will acquire the new information as part of the

MMU's normal response to access misses. Address translation proceeds as

follows.

Given a virtual

address, the MMU looks in the TLB for the referenced page. IT the page table

entry for this page is found in the TLB, the physical address is obtained

immediately. If there is a miss in the TLB, then the required entry is obtained

from the page table in the main memory and the TLB is updated. When a program

generates an access request to a page that is not in the main memory, a page

fault is said to have occurred. The whole page must be brought from the disk

into the memory before access can proceed. When it detects a page fault, the

MMU

asks the operating

system to intervene by raising an exception (interrupt). Processing of the

active task is interrupted, and control is transferred to the operating system.

The operating system

then copies the requested page from the disk into the main memory and returns

control to the interrupted task. Because a long delay occurs while the page

transfer takes place, the operating system may suspend execution of the task that

caused the page fault and begin execution of another task whose pages are in

the main memory.

It is essential to

ensure that the interrupted task can continue correctly when it resumes

execution. A page fault occurs when some instruction accesses a memory operand

that is not in the main memory, resulting in an interruption before the

execution of this instruction is completed. Hence, when the task resumes,

either the execution of the interrupted instruction must continue from the

point of interruption, or the instruction must be restarted. The design of a

particular processor dictates which of these options should be used.

If a new page is

brought from the disk when the main memory is full, it must replace one of the

resident pages. The problem of choosing which page to remove is just as

critical here as it is in a cache, and the idea that programs spend most of

their time in a few localized areas also applies. Because main memories are

considerably larger than cache memories, it should be possible to keep

relatively larger portions of a program in the main memory. This will reduce

the frequency of transfers to and from the disk.

Concepts similar to the

FIFO, Optimal and LRU replacement algorithms can be applied to page replacement

and the control bits in the page table entries can indicate usage. One simple

scheme is based on a control bit that is set to 1 whenever the corresponding

page is referenced (accessed). The operating system occasionally clears this

bit in all page table entries, thus providing a simple way of determining which

pages have not been used recently.

A modified page has to

be written back to the disk before it is removed from the main memory. It

isimportant to note that the write-through protocol, which is useful in the

framework of cache memories, is not suitable for virtual memory. The access

time of the disk is so long that it does not make sense to access it frequently

to write small amounts of data. The address translation process in the MMU

requires some time to perform, mostly dependent on the time needed to look up

entries in the TLB. Because of locality of reference, it is likely that many

successive translations involve addresses on the same page. This is

particularly evident in fetching instructions. Thus, we can reduce the average

translation time by including one or more special registers that retain the

virtual page number and the physical page frame of the most recently performed

translations. The information in these registers can be accessed more quickly

than the TLB.

Related Topics