Chapter: Digital Principles and System Design : Memory and Programmable Logic

Programmable Logic Devices

PROGRAMMABLE LOGIC DEVICES

ü PROGRAMMABLE LOGIC ARRAY

There are a wide variety of ICs that can

have their logic function “programmed” into them

after they are manufactured. Most of these

devices use technology that also allows the function to be reprogrammed, which

means that if you find a bug in your design.

Programmable logic arrays (PLAs) were the first programmable

logic devices. PLAs contained a two-level structure of AND and OR gates with

user-programmable connections. Using this structure, a designer could

accommodate any logic function up to a certain level of complexity using the

well-known theory of logic synthesis and minimization

PLA structure was enhanced and PLA costs were reduced with the

introduction of programmable array logic (PAL) devices. Today, such devices are

generically called programmable logic devices (PLDs), and

are the “MSI” of programmable logic

industry.

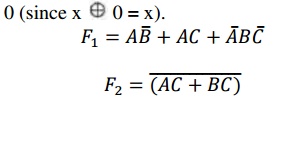

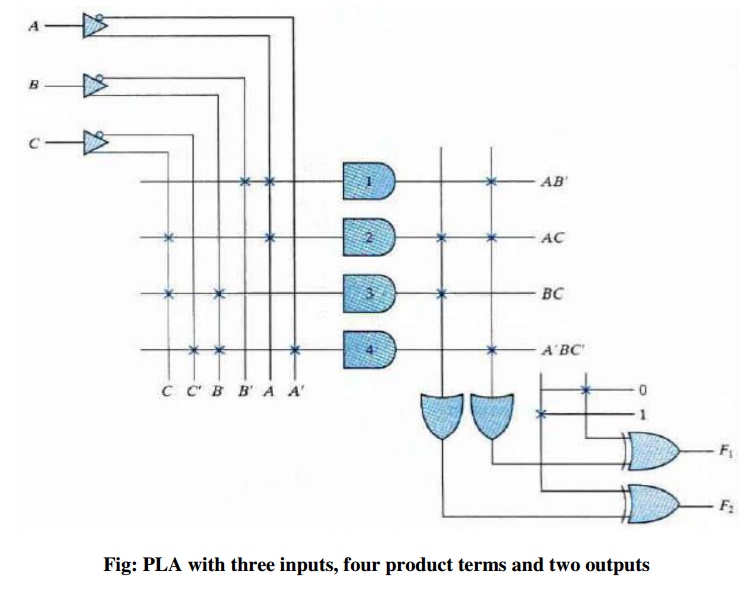

The PLA is similar in concept to the PROM, except that the PLA does not provide full decoding of the variables and does not generate all the minterms. The decoder is replaced by an array of AND gates that can be programmed to generate any product term of the input variables. The product terms are then connected to OR gates to provide the sum of products for the required Boolean functions. The output is inverted when the XOR input is connected to

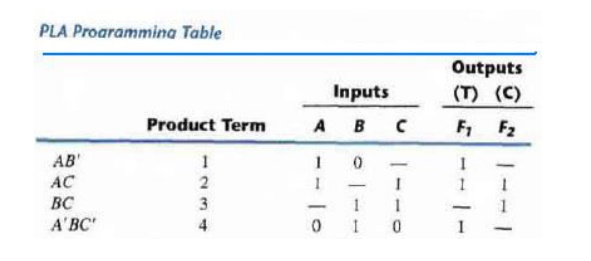

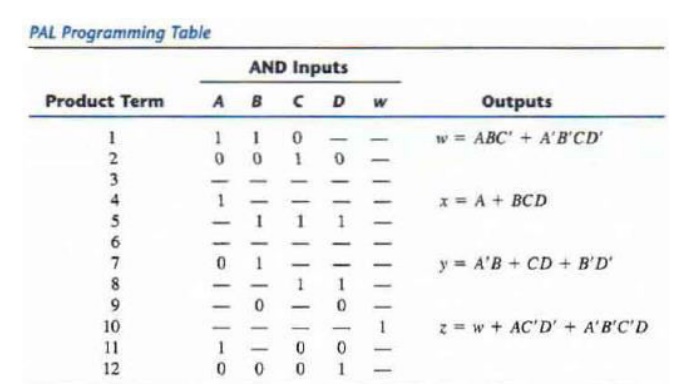

The fuse map of a PLA can be

specified in a tabular form. The first section lists the product terms

numerically. The second section specifies the required paths between inputs and

AND gates. The third section specifies the paths between the AND and OR gates.

For each output variable, we may have a T'(for true) or C (for complement) for

programming the XOR gate.

For each product term, the inputs are marked with 1, 0, or -

(dash). If a variable in the product term appears in the form in which it is

true, the corresponding input variable is marked with a 1. If it appears

complemented, the corresponding input variable is marked with a 0. If the

variable is absent from the product term, it is marked with a dash.

ü PROGRAMMABLE ARRAY LOGIC

The PAL is a programmable logic device with a fixed OR array

and a programmable AND array. Because only the AND gates are programmable, the

PAL is easier to program than but is not as flexible as the PLA.

There are four sections in the unit each composed of an AND-OR

array that is three wide, the term used to indicate that there are three

programmable AND gates in each section and one fixed OR gate. Each AND gate has

10 programmable input connections, shown in the diagram by 10 vertical lines

intersecting each horizontal line. The horizontal line symbolizes the

multiple-input configuration of the AND gate. One of the outputs is connected

to a buffer-inverter gate and then fed back into two inputs of the AND gates.

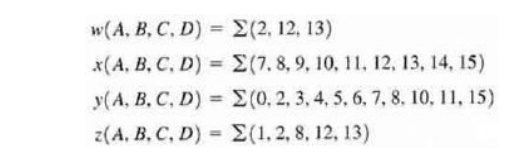

As an example of using a PAL in the design of a combinational

circuit, consider me following Boolean functions, given in sum-of-minterms

form:

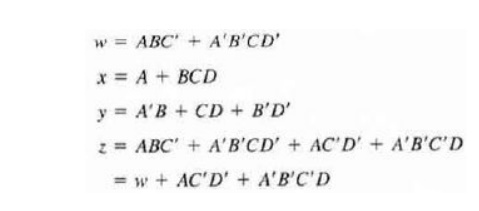

Simplifying the four functions to a minimum number of terms

results in the following Boolean functions:

Note that the function for z has four product terms. The

logical sum of two of these terms is equal to w. By using w, it is possible to

reduce the number of terms for z from four to three.

Related Topics