Chapter: Electronic Circuits : BJT Amplifiers

Transistorised Differential Amplifier

Transistorised Differential

Amplifier

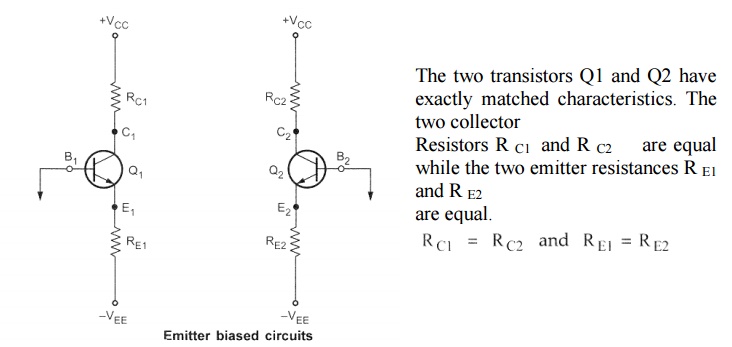

The

transistorised differential amplifier basically uses the emitter biased

circuits which are identical in characteristics. Such two identical emitter

biased circuits are

The

magnitudes of + Vcc and – V EE are also same. The differential

amplifier can be obtained by using such two emitter biased circuits. This is

achieved by connecting emitter E1 of Q1 to the emitter E2 of Q2. Due to this, R

E1 appears in parallel with R E2 and the combination can

be replaced by a single resistance denoted as R E. The base B1

of Q1 is connected to the input 1 which is V S1 while the base B 2

of Q2 is connected to the input 2 which is Vs2. The supply voltages

are measured with respect to ground. The balanced output is taken between the

collector C1 of Q1 and the collector C2 of Q 2. Such an amplifier is

called emitter coupled differential amplifier. The two collector resistances

are same hence can be denoted as R C..

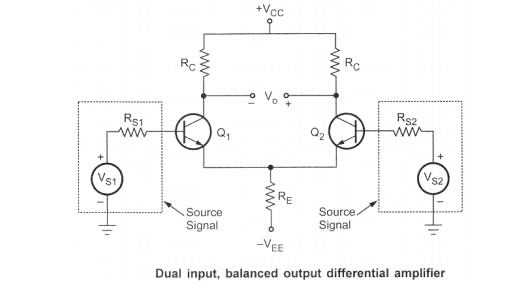

The

output can be taken between two collectors or in between one of the two

collectors and the ground. When the output is taken between the two collectors,

none of them is grounded then it is called balanced output, double ended output

or floating output. When the output is taken between any of the collectors and

the ground, it is called unbalanced output or single ended output. The complete

circuit diagram of such a basic dual input, balanced output differential

amplifier is shown in the Fig.

As the

output is taken between two output terminals, none of them is grounded, it is

called balanced output differential amplifier.

Let us

study the circuit operation in the two modes namely

• Differential

mode operation

• Common

mode operation

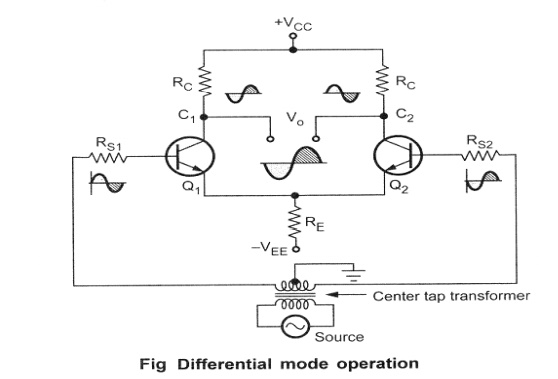

1. Differential Mode Operation

In the

differential mode, the two input signals are different from each other.

Consider the two input signals which are same in magnitude but 180" out of

phase. These signals, with opposite phase can be obtained from the center tap

transformer. The circuit used in differential mode operation is shown in the

Fig

Assume

that the sine wave on the base of Q 1is positive going while on the

base of Q 2 is negative going. With a positive going signal on the

base of Q 1 , m amplified negative going signal develops on the

collector of Q1. Due to positive going signal, current through R E

also increases and hence a positive going wave is developed across R E.

Due to negative going signal on the base of Q2, an amplified positive going

signal develops on the collector of Q 2 . And a negative going

signal develops across R E, because of emitter follower action of Q 2.

So signal voltages across R E, due to the effect of Q1 and Q2 are

equal in magnitude and 180o out of phase, due to matched pair of transistors.

Hence these two signals cancel each other and there is no signal across the

emitter resistance. Hence there is no a.c. signal current flowing through the

emitter resistance. Hence R E in this case does not introduce

negative feedback. While Vo is the output taken across collector of Q1 and

collector of Q 2. The two outputs on collector L and 2 are equal in

magnitude but opposite in polarity. And Vo is the difference between these two

signals, e.g. +10 - (-10) = + 20.

Hence the

difference output Vo is twice as large as the signal voltage from either

collector to ground

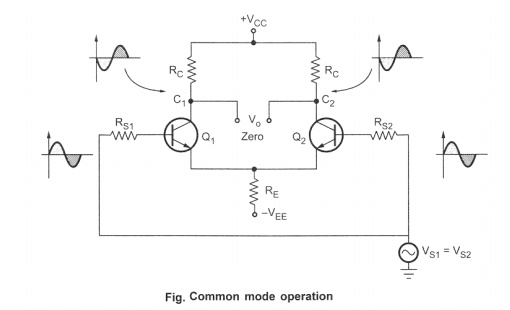

2. Common Mode Operation

In this

mode, the signals applied to the base of Q1 and Q2 are derived from the same

source. So the two signals are equal in magnitude as well as in phase. The

circuit diagram is shown in the Fig.

In phase

signal voltages at the bases of Q1 and Q2 causes in phase signal voltages to

appear across R E, which add together. Hence R E carries

a signal current and provides a negative feedback. This feedback reduces the

common mode gain of differential amplifier.

While the

two signals causes in phase signal voltages of equal magnitude to appear across

the two collectors of Q 1 and Q2. Now the output voltage is the

difference between the two collector voltages, which are equal and also same in

phase, Eg. (20) - (20) = 0. Thus the difference output Vo is almost zero,

negligibly small. ideally it should be zero.

Related Topics