Chapter: Microprocessor and Microcontroller : I/O Interfacing

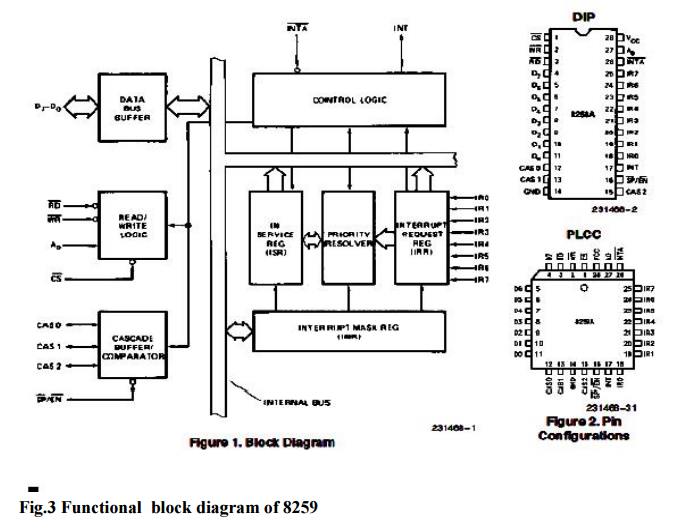

Interrupt controller Intel 8259A

Interrupt Controller

The Intel

8259A Programmable Interrupt Controller handles up to eight vectored priority

interrupts for the CPU. It is cascadable for up to 64 vectored priority

interrupts without additional circuitry. It is packaged in a 28-pin DIP, uses

NMOS technology and requires a single a5V supply. Circuitry is static,

requiring no clock input.

The 8259A

is designed to minimize the software and real time overhead in handling

multi-level priority interrupts.

It has

several modes, permitting optimization for a variety of system requirements.

The 8259A is fully upward compatible with the Intel 8259. Software originally

written for the 8259 will operate the 8259A in all 8259 equivalent modes

(MCS-80/85, Non-Buffered and Edge Triggered).

The

microprocessor will be executing its main program and only stop to service

peripheral devices when it is told to do so by the device itself. In effect,

the method would provide an external asynchronous input that would inform the

processor that it should complete whatever instruction that is currently being

executed and fetch a new routine that will service the requesting device. Once

this servicing is complete, however, the processor would resume exactly where

it left off.This method is called Interrupt.

System

throughput would drastically increase, and thus more tasks could be assumed by

the microcomputer to further enhance its cost effectiveness. The Programmable

Interrupt Controller (PIC) functions as an overall manager in an

Interrupt-Driven system environment. It accepts requests from the peripheral

equipment, determines which of the incoming requests is of the highest

importance (priority), ascertains whether the incoming request has a higher

priority value than the level currently being serviced, and issues an interrupt

to the CPU based on this determination.

Each

peripheral device or structure usually has a special program or ``routine''

that is associated with its specific functional or operational requirements;

this is referred to as a ``service routine''. The PIC, after issuing an

Interrupt to the CPU, must somehow input information into the CPU that can

``point'' the Program Counter to the service routine associated with the

requesting device. This ``pointer'' is an address in a vectoring table and will

often be referred to, in this document, as vectoring data.

ü Interrupt request register (IRR)

AND in-service register (ISR):

The

interrupts at the IR input lines are handled by two registers in cascade, the

Interrupt Request Register (IRR) and the In-Service (ISR). The IRR is used to

store all the interrupt levels which are requesting service; and the ISR is

used to store all the interrupt levels which are being serviced.

ü Priority resolver

This

logic block determines the priorites of the bits set in the IRR. The highest

priority is selected and strobed into the corresponding bit of the ISR during

INTA pulse.

ü Interrupt mask register (IMR)

The IMR

stores the bits which mask the interrupt lines to be masked. The IMR operates

on the IRR.Masking of a higher priority input will not affect the interrupt

request lines of lower quality.

ü INT (INTERRUPT)

This

output goes directly to the CPU interrupt input. The VOH level on this line is

designed to be fully compatible with the 8080A, 8085A and 8086 input levels.

ü INTA (INTERRUPT ACKNOWLEDGE)

INTA

pulses will cause the 8259A to release vectoring information onto the data bus.

The format of this data depends on the system mode (mPM) of the 8259A.

ü Data bus buffer

This

3-state, bidirectional 8-bit buffer is used to interface the 8259A to the

system Data Bus. Control words and status information are transferred through

the Data Bus Buffer.

ü Read/write control logic

The

function of this block is to accept OUTput commands from the CPU. It contains

the Initialization Command Word (ICW) registers and Operation Command Word

(OCW) registers

which

store the various control formats for device operation. This function block

also allows the status of the 8259A to be transferred onto the Data Bus.

ü CS (CHIP SELECT)

A LOW on

this input enables the 8259A. No reading or writing of the chip will occur

unless thedevice is selected.

ü WR (WRITE)

A LOW on

this input enables the CPU to write control words (ICWs and OCWs) to the 8259A.

ü RD (READ)

A LOW on

this input enables the 8259A to send the status of the Interrupt Request

Register (IRR),In Service Register (ISR), the Interrupt Mask Register (IMR), or

the Interrupt level onto the Data Bus.

ü A0

This

input signal is used in conjunction with WR and RD signals to write commands

into the various command registers, as well as reading the various status

registers of the chip. This line can be tieddirectly to one of the address

lines.

Interrupt sequence

The

powerful features of the 8259A in a microcomputer system are its

programmability and the interrupt routine addressing capability. The latter

allows direct or indirect jumping to the specific interrupt routine requested

without any polling of the interrupting devices. The normal sequence of events

during an interrupt depends on the type of CPU being used.

The

events occur as follows:

1. One or

more of the INTERRUPT REQUEST lines (IR7±0) are raised high, setting the

corresponding IRR bit(s).

2. The 8259A

evaluates these requests, and sends an INT to the CPU, if appropriate.

3. The CPU

acknowledges the INT and responds with an INTA pulse.

4. Upon

receiving an INTA from the CPU group, the highest priority ISR bit is set, and

the corresponding IRR bit is reset. The 8259A will also release a CALL

instruction code (11001101) onto the 8-bit Data Bus through its D7±0 pins.

5. This CALL

instruction will initiate two more INTA pulses to be sent to the 8259A from the

CPU group.

6. These two

INTA pulses allow the 8259A to release its preprogrammed subroutine address

onto the Data Bus. The lower 8-bit address is released at the first INTA pulse

and the higher 8-bit address is released at the second INTA pulse.

7. This

completes the 3-byte CALL instruction released by the 8259A. In the AEOI mode

the ISR bit is reset at the end of the third INTA pulse. Otherwise, the ISR bit

remains set until an appropriate EOI command is issued at the end of the

interrupt sequence. The events occurring in an 8086 system are the same until

step 4.

8. Upon

receiving an INTA from the CPU group, the highest priority ISR bit is set and

the corresponding IRR bit is reset. The 8259A does not drive the Data Bus

during this cycle.

9. The 8086

will initiate a second INTA pulse. During this pulse, the 8259A releases an

8-bit pointer onto the Data Bus where it is read by the CPU.

This

completes the interrupt cycle. In the AEOI mode the ISR bit is reset at the end

of the second INTA pulse. Otherwise, the ISR bit remains set until an

appropriate EOI command is issued at the end of the interrupt subroutine. If no

interrupt request is present at step 4 of either sequence (i.e., the request was

too short in duration) the 8259A will issue an interrupt level 7. Both the

vectoring bytes and the CAS lines will look like an interrupt level 7 was

requested. When the 8259A PIC receives an interrupt, INT becomes active and an

interrupt acknowledge cycle is started. If a higher priority interrupt occurs

between the two INTA pulses, the INT line goes inactive immediately after the

second INTA pulse. After an unspecified amount of time the INT line is

activated again to signify the higher priority interrupt waiting for service.

Related Topics