Chapter: Principles of Compiler Design : Code Generation

Target Machine

TARGET MACHINE

Familiarity with the target machine and its instruction set is a prerequisite for

designing a good code generator.

The target computer is a byte-addressable machine with 4 bytes to a word.

It has ngeneral-purpose registers, R0, R1, . . . ,

Rn-1.

It has two-address instructions of the form:

o

op source, destination

o

where, opis an op-code, and sourceanddestinationaredatafields.

·

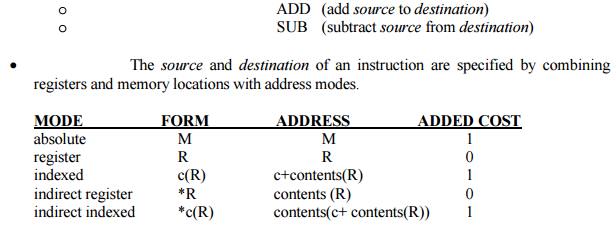

It has the following op-codes :

o

MOV (move sourcetodstination)

For

example : MOV R0, M stores contents of Register R0 into

memory location M.

Instruction costs :

• Instruction

cost = 1+cost for source and destination address modes. This cost corresponds

to the length of the instruction.

• Address

modes involving registers have cost zero.

• Address

modes involving memory location or literal have cost one.

• Instruction

length should be minimized if space is important. Doing so also minimizes the

time taken to fetch and perform the instruction.

For example : MOV R0,

R1 copies the contents of register R0 into R1. It has cost one, since

occupies only one word of memory.

• The three-address

statement a : = b + c can be implemented by many different instruction

sequences :

i)

MOV b, R0

ADD c, R0 cost = 6 MOV R0, a

ii)

MOV b, a

ADD

c, a cost = 6

iii) Assuming R0, R1 and R2 contain the addresses of

a, b, and c : MOV *R1, *R0

ADD

*R2, *R0 cost = 2

• In order to generate

good code for target machine, we must utilize its addressing capabilities

efficiently.

Related Topics