Chapter: Advanced Computer Architecture : Multiple Issue Processors

IA-64 Architecture

IA-64 ARCHITECTURE

It is a

RISC-style, register-register instruction set architecture. Designed to support

compiler-based exploitation of ILP.

1. COMPONENTS OF IA-64 REGISTER

STATE

128

64-Bit

general purpose registers

128

82-Bit floating-point register (provides 2 extra bits over std. 80-bit IEEE

format)

64

1-Bit predicate registers

8

64-Bit branch registers, used for indirect branches

Various

registers used for system control, memory mapping, performance

counters, etc.

2. REGISTER MECHANISM

0-31 → Accessible

Registers

32-128 → Used

as a register stack

CFM → Set of registers to

be used by a given procedure. (Current FraMe

Point)

Integer

register

Floating

point register

Predicate

register

3. REGISTER

A frame

is created for a called procedure, by renaming the registers in hardware.

Ø Frame has local area and output area parts.

Ø The

“alloc” instruction specifies the size of these areas.

To handle

the over flow of the register stack,

special h/w called the register stack engine

is used.

4. INSTRUCTION FORMAT

Ø Supports

for both Explicit Parallelism and Implicit Parallelism

Ø Benefits

of VLIW approach-implicit parallelism among operations in an instruction and

fixed formatting of the operation fields.

Ø It can be

achieved by relying on the compiler to detect ILP and schedule instructions

into parallel instruction slots.

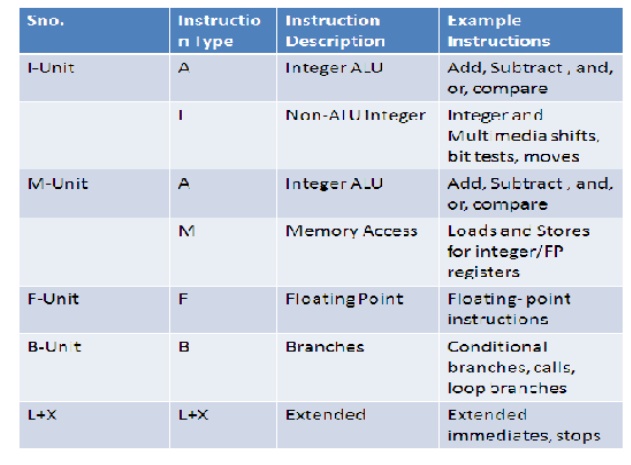

5. FIVE EXECUTION UNIT SLOTS

6. BENEFITS OF IA-64

1) Implicit parallelism

Ø By

placing instructions into instruction groups

2) Ease of

Instruction decode

Ø By bundle

3) Predication

4) Speculation

5) Memory

Reference

7. Instruction Group:

Ø It is a

sequence of consecutive instructions with no register data dependences among

them.

Ø If

sufficient hardware resources existed and if any dependences through memory

were preserved, then all the instructions in a group could be executed in

parallel.

8. Bundles

Each

bundle consists of a 5-bit template field and three instructions, each 41 bits

in length. Template field specifies what types of execution units each

instruction in the bundle requires.

9. Predication

Ø An

instruction is predicated by a predicate register, whose identity is placed in

the lower 6 bits of each instruction field.

Ø Predicate

registers are the set using compare and test instructions

Ø It allows

multiple comparisons to be done in one instruction.

10. Speculation:

Ø It

supports for control speculation

Ø That is

deals with deferring exception for speculated instruction, memory reference

speculation and thus supports speculation of load instructions.

11. Memory reference

Ø It uses

the concept of advanced loads

Ø Advanced

load is a load that has been speculatively moved above store instructions on

which it is potentially dependent

Ø The instruction

ld.a is used for advanced load, which is to speculatively perform a load.

Ø Execution

creates an entry called ALAT (Advanced Load Address Table).

Ø ALAT

stores both the register destination of the load and the address of the

accessed memory location.

Ø When a

store is executed, an associative lookup against the active ALAT entries is

performed.

Related Topics