Chapter: Embedded and Real Time Systems : Case Study

Hardware and Software Co-Design- Embedded and Real Time Systems

HARDWARE

AND SOFTWARE CO-DESIGN:

Distributed embedded systems can be organized in many different ways

depending upon the needs of the application and cost constraints. One good way

to understand possible architectures is to consider the different types of

interconnection networks that can be used.

A point-to-point link establishes a connection between exactly

two PEs. Point to point links is simple to design precisely because they deal

with only two components. We do not have to worry about other PEs interfering

with communication on the link.

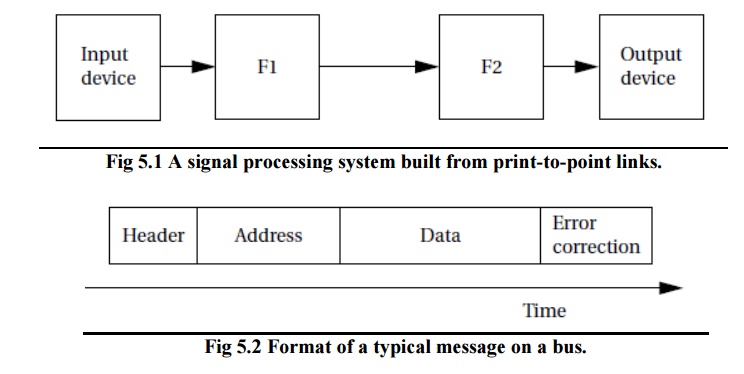

Figure 5.1 shows a simple example of a distributed embedded system built

from point-to-point links. The input signal is sampled by the input device and

passed to the first digital filter, F1, over a point-to-point link. The

results of that filter are sent through a second point-to-point link to filter F2. The results in turn are sent to the

output device over a third point-to-point link.

A digital filtering system requires that its outputs arrive at strict

intervals, which means that the filters must process their inputs in a timely

fashion. Using point-to-point connections allows both F1 and F2 to receive a

new sample and send a new output at the same time without worrying about

collisions on the communications network.

It is possible to build a full-duplex, point-to-point

connection that can be used for simultaneous communication in both directions

between the two PEs. (A halfduplex connection allows for only one-way

communication.)

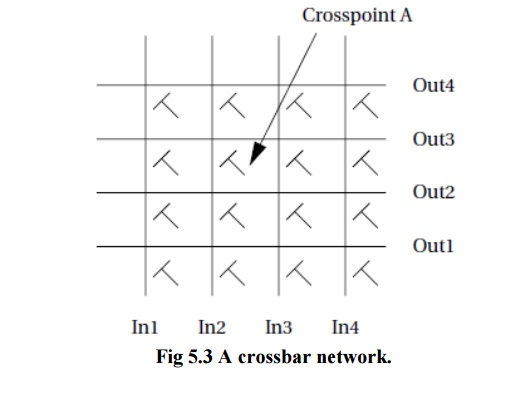

A bus is a more general form of network since it

allows multiple devices to be connected to it. Like a microprocessor bus, PEs

connected to the bus have addresses. Communications on the bus generally take

the form of packets as illustrated in Figure 5.2. A packet contains an

address for the destination and the data to be delivered.

It frequently includes error detection/correction information such as

parity. It also may include bits that serve to signal to other PEs that the bus

is in use, such as the header shown in the figure.

The data to be transmitted from one PE to another

may not fit exactly into the size of the data payload on the packet. It

is the responsibility of the transmitting PE to divide its data into packets;

the receiving PE must of course reassemble the complete data message from the

packets.

Distributed system buses must be arbitrated to control simultaneous

access, just as with microprocessor buses. Arbitration scheme types are

summarized below.

Fixed-priority

arbitration always gives priority to competing devices in the

same way. If a high-priority and a

low-priority device both have long data transmissions ready at the same time,

it is quite possible that the low-priority device will not be able to transmit

anything until the high-priority device has sent all its data packets.

Fair

arbitration schemes make sure that no device is starved. Round-robin

arbitration is the most commonly used of the fair arbitration schemes.

The PCI bus requires that the arbitration scheme used on the bus must be fair,

although it does not specify a particular arbitration scheme. Most

implementations of PCI use round-robin arbitration.

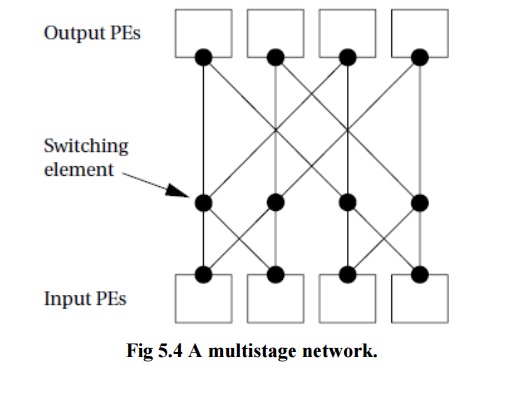

A bus has limited available bandwidth. Since all devices connect to the

bus, communications can interfere with each other. Other network topologies can

be used to reduce communication conflicts. At the opposite end of the

generality spectrum from the bus is the crossbar network shown in Figure

5.3.

A crossbar not only allows any input to be

connected to any output, it also allows all combinations of input/output

connections to be made. Thus, for example, we can simultaneously connect in1 to out4, in2 to out3, in3 to out2, and in4 to out1 or any other combinations of inputs.

Many other networks have been designed that provide varying amounts of

parallel communication at varying hardware costs. Figure 5.4 shows an example multistage

network. The crossbar of Figure 5.3 is a direct network in which

messages go from source to destination without going through any memory

element.

Multistage networks have intermediate routing nodes to guide the data

packets.

Most networks are blocking, meaning that there are

some combinations of sources and destinations for which messages cannot be

delivered simultaneously.

A bus is a maximally blocking network since any message on the bus

blocks messages from any other node. A crossbar is non-blocking.

In general, networks differ from microprocessor buses in how they

implement communication protocols. Both need handshaking to ensure that PEs do

not interfere with each other. But in most networks, most of the protocol is

performed in software.

Microprocessors rely on bus hardware for fast

transfers of instructions and data to and from the CPU. Most embedded network

ports on microprocessors implement the basic communication functions (such as

driving the communications medium) in hardware and implement many other

operations in software.

An alternative to a non-bus network is to use multiple networks. As with

PEs, it may be cheaper to use two slow, inexpensive networks than a single high

performance, expensive network.

If we can segregate critical and noncritical communications onto

separate networks, it may be possible to use simpler topologies such as buses.

Many systems use serial links for low-speed communication and CPU buses for

higher speed and volume data transfers.

Related Topics